# **PART NO.** MVR0603-100E2R5

### 1. Electrical Specification

#### 1-1 Test condition

Varistor voltage In = 1 mA DC

Leakage current Vdc = 10 V DC

Maximum clamping voltage Ic = 1 A

Rated peak single pulse transient current  $8/20~\mu s$  waveform, +/- each 1 time induce

Capacitance 10/1000  $\mu$ s waveform Insulation resistance after reflow soldering f = 1MHz, Vrms = 0.5 V

Soldering paste : Tamura (Japan) RMA-20-21L

Stencil : SUS, 120  $\mu$ m thickness

Reflow soldering condition Pad size : 0.8 (Width) x 0.9 (Length)

0.8 (Distance between pads)

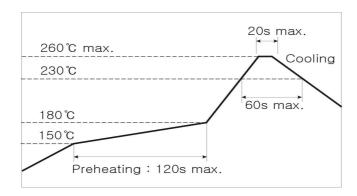

Soldering profile : 260 $\pm 5$  °C, 5 sec.

### 1-2 Electrical specification

| Maximum allowable continuous DC voltage                | 10          | V                  |         |

|--------------------------------------------------------|-------------|--------------------|---------|

| trigger voltage / Varistor voltage / breakdown voltage | 22-34       | V                  |         |

| Maximum clamping voltage                               | 60          | V                  | Maximum |

| Rated peak single pulse transient current 1            |             |                    | Maximum |

| Nonlinearity coefficient                               | > 12        |                    |         |

| Leakage current at continuous DC voltage               | < 0.1       | $\mu$ A            |         |

| Response time                                          | < 0.5       | ns                 |         |

| Varistor voltage temperature coefficient               | < 0.05      | %/℃                |         |

| Capacitance measured at 1MHz                           | 2.5         | pF                 | Typical |

| Capacitance tolerance                                  | $\pm 30$    | %                  |         |

| Insulation resistance after reflow soldering on PCB    | > 10        | $\mathbf{M}\Omega$ |         |

| Operating ambient temperature                          | -55 to +125 | ${\mathbb C}$      |         |

| Storage temperature                                    | -55 to +125 | ${\mathbb C}$      |         |

## 1-3 Reliability testing procedures

| Reliability parameter                                                                                                                                                                                                                                             | Test                        | Test methods and remarks                                                                                                                                     | Test requirement                        |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|

| Pulse current capability                                                                                                                                                                                                                                          | Imax<br>8/20 μs             | IEC 1051-1, Test 4.5.  10 pulses in the same direction at 2 pulses per minute at maximum peak current                                                        | d   Vn   /Vn ≤ 10%<br>no visible damage |  |

| Electrostatic<br>discharge<br>capability                                                                                                                                                                                                                          | ESD<br>C=150 pF,<br>R=330 Ω | IEC 1000-4-2  Each 10 times in positive/negative direction in 10 sec at 8KV contact discharge (Level 4)                                                      |                                         |  |

| Step 2 : Max. +125 °C,  Number of cycles: 30 tim  Low temperature    IEC 68-2-1     Place the chip at -40 ±   12hrs. Remove and place room temp. condition, the left temperature     IEC 68-2-2     Place the chip at 125 ±   24hrs. Remove and place temperature |                             | Condition for 1 cycle<br>Step 1 : Min. −40 °C, 30 ± 3 min.<br>Step 2 : Max. +125 °C, 30 ± 3 min.                                                             | d   Vn   /Vn ≤ 5%<br>no visible damage  |  |

|                                                                                                                                                                                                                                                                   |                             |                                                                                                                                                              | d   Vn   /Vn ≤ 5%<br>no visible damage  |  |

|                                                                                                                                                                                                                                                                   |                             | IEC 68-2-2  Place the chip at $125\pm5$ °C for $1000\pm24$ hrs. Remove and place for $24\pm2$ hrs at room temp. condition, then measure                      | d   Vn   /Vn ≤ 5%<br>no visible damage  |  |

|                                                                                                                                                                                                                                                                   | Heat resistance             | IEC 68-2-3 Apply the rated voltage for $1000\pm48 hrs$ at $85\pm3\%$ . Remove and place for $24\pm2 hrs$ at room temp. condition, then measure               | d   Vn   /Vn ≤ 5%<br>no visible damage  |  |

|                                                                                                                                                                                                                                                                   | Humidity<br>resistance      | IEC 68-2-30 Place the chip at $40\pm2\%$ and 90 to 95% humidity for $1000\pm24$ hrs. Remove and place for $24\pm2$ hrs at room temp. condition, then measure | d   Vn   /Vn ≤ 10%<br>no visible damage |  |

|                                                                                                                                                                                                                                                                   | Pressure cooker<br>test     | Place the chip at 2 atm, 120 °C, 85%RH for 60 hrs. Remove and place for 24 ± 2hrs at room temp. condition, then measure                                      | d   Vn   /Vn ≤ 10%<br>no visible damage |  |

|                                                                                                                                                                                                                                                                   | Operating life              | Apply the rated voltage for 1000±48hrs at 125±3℃. Remove and place for 24± 2hrs at room temp. condition, then measure                                        | d   Vn   /Vn ≤ 10%<br>no visible damage |  |

| Mechanical<br>Reliability | Solderability                                                             | IEC 68-2-58 Solder bath method, 230±5℃, 2s                                                                | At least 95% of terminal electrode is covered by new solder |  |

|---------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|

|                           | Resistance to                                                             | IEC 68-2-58                                                                                               | d   Vn   /Vn≤5%                                             |  |

| soldering heat            | Solder bath method, $260\pm5$ °C, $10\pm0.5$ s, $270\pm5$ °C, $3\pm0.5$ s | no visible damage                                                                                         |                                                             |  |

|                           | Bending strength                                                          | IEC 68-2-21                                                                                               | d $ Vn /Vn \le 5\%$                                         |  |

|                           |                                                                           | Warp:2mm, Speed:0.5mm/sec, Duration: 10sec. The measurement shall be made with board in the bent position | no visible damage                                           |  |

|                           | Adhesive strength                                                         | IEC 68-2-22                                                                                               | Strength>10 N                                               |  |

|                           |                                                                           | Applied force on SMD chip by fracture from PCB                                                            | no visible damage                                           |  |

## 2. Material Specification

Body ZnO based ceramics

Internal electrode Silver – Palladium

External electrode Silver – Nickel – Tin

Thickness of Ni/Sn plating layer Nickel  $> 1 \mu m$ , Tin  $> 2 \mu m$

## 3. Dimension Specification

| Size | L(mm)          | W(mm)          | T(mm) | M(mm)           |

|------|----------------|----------------|-------|-----------------|

| 0402 | $1.0 \pm 0.10$ | $0.5 \pm 0.10$ | ≤ 0.6 | $0.20 \pm 0.10$ |

| 0603 | 1.6±0.15       | $0.8 \pm 0.15$ | ≤ 0.9 | $0.35 \pm 0.10$ |

## 4. Soldering Recommendations

### 4-1 Soldering profile

### 4-1-1 Pb free solder paste

### 4-1-2 Repair soldering

- Allowable time and temperature for making correction with a soldering iron : 350  $\pm$  10  $^{\circ}$ C, 3 sec.

- Optimum solder amount when corrections are made using a soldering iron

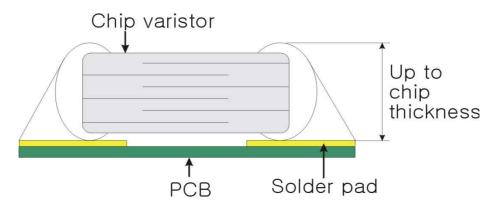

## 4-2 Soldering guidelines

- Our chip varistors are designed for reflow soldering only. Do not use flow soldering

- Use non-activated flux (CI content 0.2% max.)

- Follow the recommended soldering conditions to avoid varistor damage.

### 4-3 Solder pad layout

### 5. Storage condition

- Chip varistors can experience degradation of termination solderability when subjected to high temperature of humidity, or if exposed to sulfur or chlorine gases.

- Avoid mechanical shock (ex. Falling) to the chip varistor to prevent mechanical cracking inside of the ceramic dielectric due to its own weight.

- Use chips within 6 months.

If 6 months of more have elapsed, check solderability before use.-

### 6. Description about package label

#### Type: MVR0603-100E2R5

MVR: Series name

0603 : Chip size -0603 (1.6 x 0.8 mm) size

100 : Maximum continuous working voltage - 10Vdc

E: Product function - E for ESD

2R5: Capacitance value - means 2.5pF

#### Qunatity: 4,000 pcs

- Quantity of shipping chip varistor